北邮22信通一枚~

跟随课程进度更新北邮信通院数字系统设计的笔记、代码和文章

持续关注作者 迎接数电实验学习~

获取更多文章,请访问专栏:

北邮22级信通院数电实验_青山如墨雨如画的博客-CSDN博客

目录

一.代码部分

1.1 counter_24.v

1.2 divide.v

1.3 debounce.v

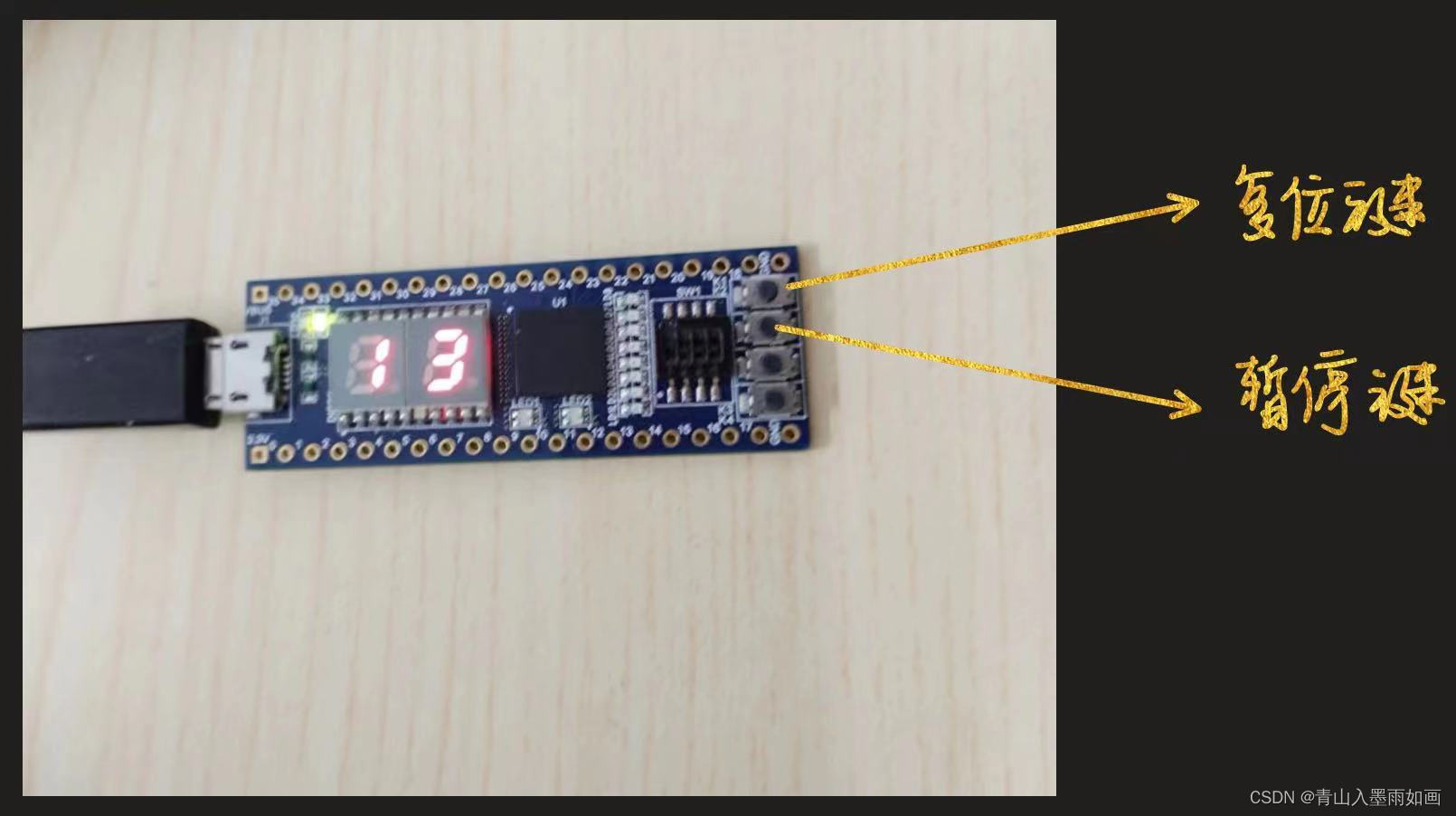

二.管脚分配

三.实验效果

一.代码部分

1.1 counter_24.v

module counter_24

(

input clk,rst,hold,

output [8:0] seg_led_1,

output [8:0] seg_led_2,

output reg [7:0] led

);

wire clk_lh;

wire hold_pulse;

reg hold_flag;

reg back_to_zero_flag;

reg [6:0] seg [16:0];

reg [3:0] cnt_ge;

reg [3:0] cnt_shi;

initial

begin

seg[0] = 7'h3f;

seg[1] = 7'h06;

seg[2] = 7'h5b;

seg[3] = 7'h4f;

seg[4] = 7'h66;

seg[5] = 7'h6d;

seg[6] = 7'h7d;

seg[7] = 7'h07;

seg[8] = 7'h7f;

seg[9] = 7'h6f;

seg[10] = 7'hf7;

seg[11] = 7'h7c;

seg[12] = 7'h39;

seg[13] = 7'h5e;

seg[14] = 7'h79;

seg[15] = 7'h71;

end

debounce debounce_1

(

.clk(clk),

.rst(rst),

.key(hold),

.key_pulse(hold_pulse)

);

divide # (.WIDTH(32),.N(12000000)) divide_1

(

.clk(clk),

.rst_n(rst),

.clkout(clk_lh)

);

always @ (posedge hold_pulse)

if(!rst==1)

hold_flag 1.2 divide.v

module divide ( clk,rst_n,clkout);

input clk,rst_n; //输入信号,其中clk连接到FPGA的C1脚,频率为12MHz

output clkout; //输出信号,可以连接到LED观察分频的时钟

//parameter是verilog里常数语句

parameter WIDTH = 3; //计数器的位数,计数的最大值为 2**WIDTH-1

parameter N = 5; //分频系数,请确保 N >1)) //N>>1表示右移一位,相当于除以2去掉余数

clk_p>1)服务器托管网)

clk_n1.3 debounce.v

module debounce (clk,rst,key,key_pulse);

parameter N = 1; //要消除的按键的数量

input clk;

input rst;

input [N-1:0] key; //输入的按键

output [N-1:0] key_pulse; //按键动作产生的脉冲

reg [N-1:0] key_rst_pre; //定义一个寄存器型变量存储上一个触发时的按键值

reg [N-1:0] key_rst; //定义一个寄存器变量储存储当前时刻触发的按键值

wire [N-1:0] key_edge; //检测到按键由高到低变化是产生一个高脉冲

//利用非阻塞赋值特点,将两个时钟触发时按键状态存储在两个寄存器变量中

always @(posedge clk or negedge rst)

begin

if (!rst) begin

key_rst 二.管脚分配

三.实验效果

数码管显示24秒倒计时,倒计时结束后所有LE服务器托管网D灯亮起。

服务器托管,北京服务器托管,服务器租用 http://www.fwqtg.net

相关推荐: 《动手学深度学习 Pytorch版》 10.7 Transformer

自注意力同时具有并行计算和最短的最大路径长度这两个优势。Transformer 模型完全基于注意力机制,没有任何卷积层或循环神经网络层。尽管 Transformer 最初是应用于在文本数据上的序列到序列学习,但现在已经推广到各种现代的深度学习中,例如语言、视觉…