各种滤波器网络仿真遇到的问题

-

各种滤波器网络仿真遇到的问题

- 1、仿真的前置问题研究

- 2、电路1仿真

- 3、电路2仿真

- 4、电路3仿真

使用软件:LTspice (ADI推荐的仿真软件)

1、仿真的前置问题研究

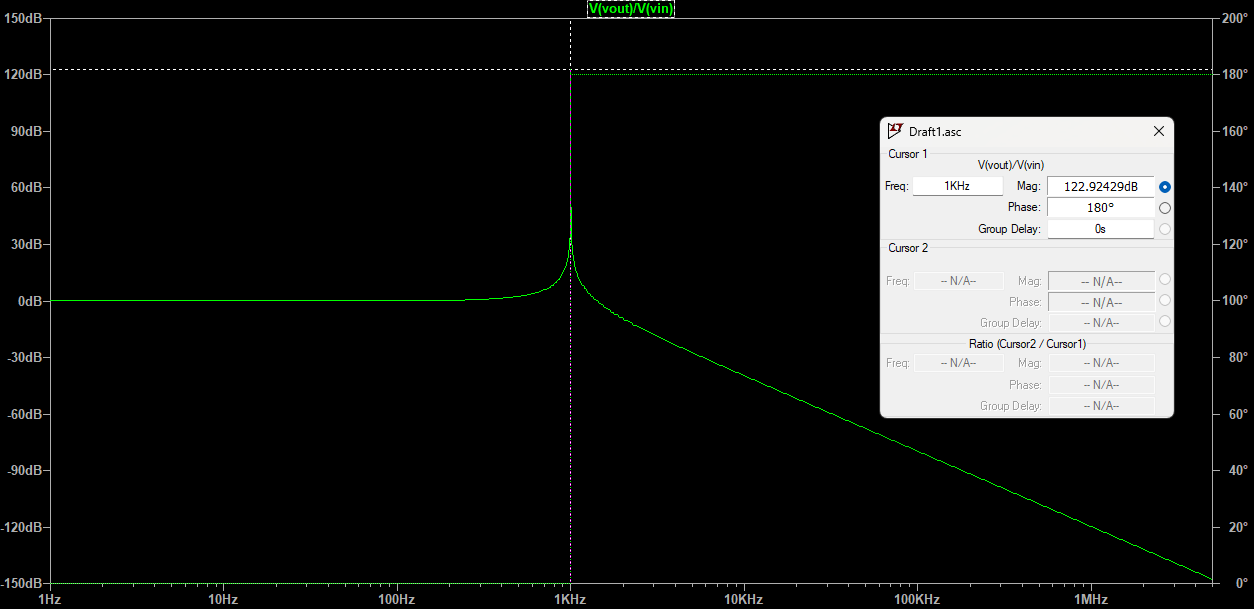

为什么在LC谐振点会产生大于0的增益?

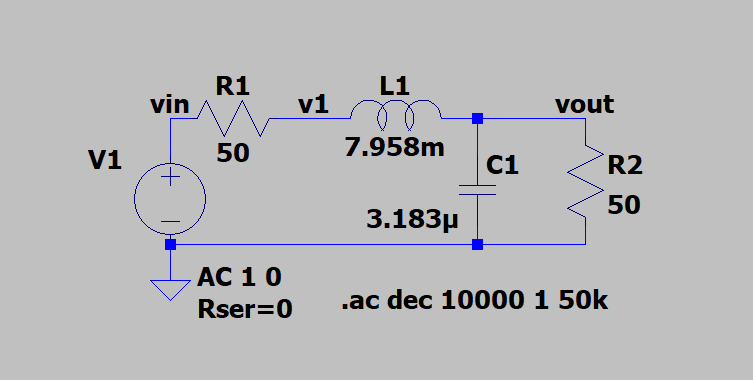

问题比较突兀,以简单的例子来验证:

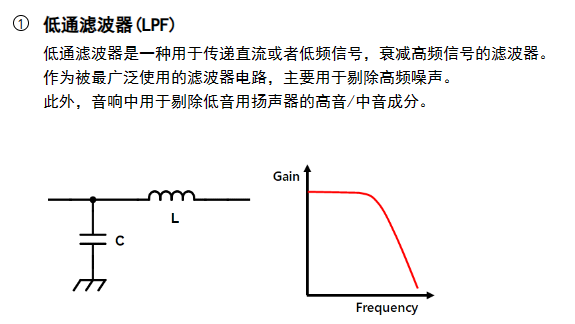

上图添加了一个简单LC低通滤波器,理想状态下LC低通滤波器的幅频响应曲线应该是一个非常平滑的曲线,如下图所示:

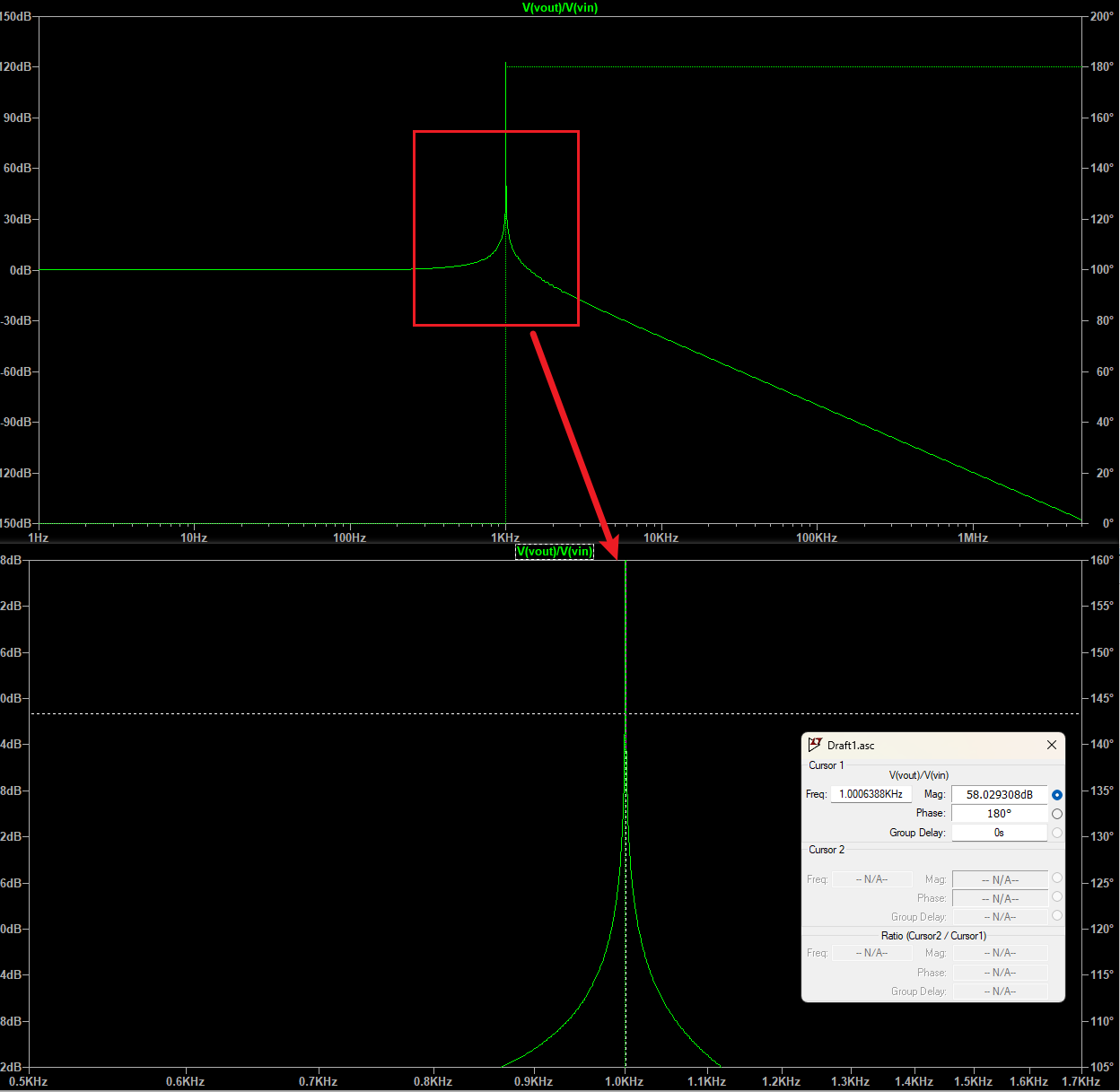

但实际上存在一个非常大的尖峰信号,我们放大一下来看:

可以看到最大值可以达到60dB的增益(实际上最大增益趋向于无穷,大小取决于采样点数和采样方法,可以见下图展示的增加采样点数的效果),这对任何无源滤波系统几乎是不可能的,当然存在即是合理,其存在的意义说明仿真的电路出了问题,那么为什么看似合理的仿真系统会出现这样的问题呢?

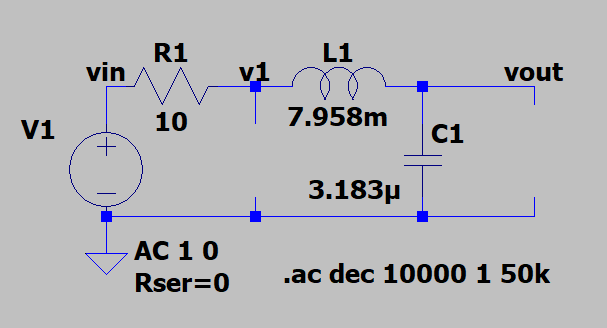

原因实际上有很多考虑,首先LTSpice的线路阻抗默认是0.1m,其次我们可以观察到尖峰的频率中心在1KHz,和电路的中LC谐振频率完全符合((f=1/2sqrt{LC})),但是这并不是巧合,我们可以简单推导一下,输入阻抗和系统谐振之间的关系,

当频率达到1Khz的时候此时L=C,电路的模型可以转化为如下(注意此处测量的Vin位置变化了):

电路的阻抗如下:

]

而此时容抗和感抗完全一致:

也就是说:

]

整个电路呈现电阻特性,即(Z=R_1),

所以整个回路电流等于输入电压除以信号源内阻,输出电压等于电容两端的电压 ,等于电流乘以容抗,最后计算出来是等于:

V_{out} = U_c = I *X_c = frac{U_i }{R_s} * frac{1 }{2pi f_0 c} = frac{U_i }{R_s} * sqrt{frac{L}{C}}

]

也就是说系数(frac{1}{R_s}sqrt{frac{L}{C}})决定了输出电压的大小,也就是目前Vout和Vin的比值,那么为什么在上文中Vout会和V1的比值变成一个很大的数呢?(注此处(R_s = R_1))

我们测量一下就知道,实际上此时回路处于短路状态,只有线阻的电压大小,测量可知:

所以Vout服务器托管网/V1趋近于无穷。

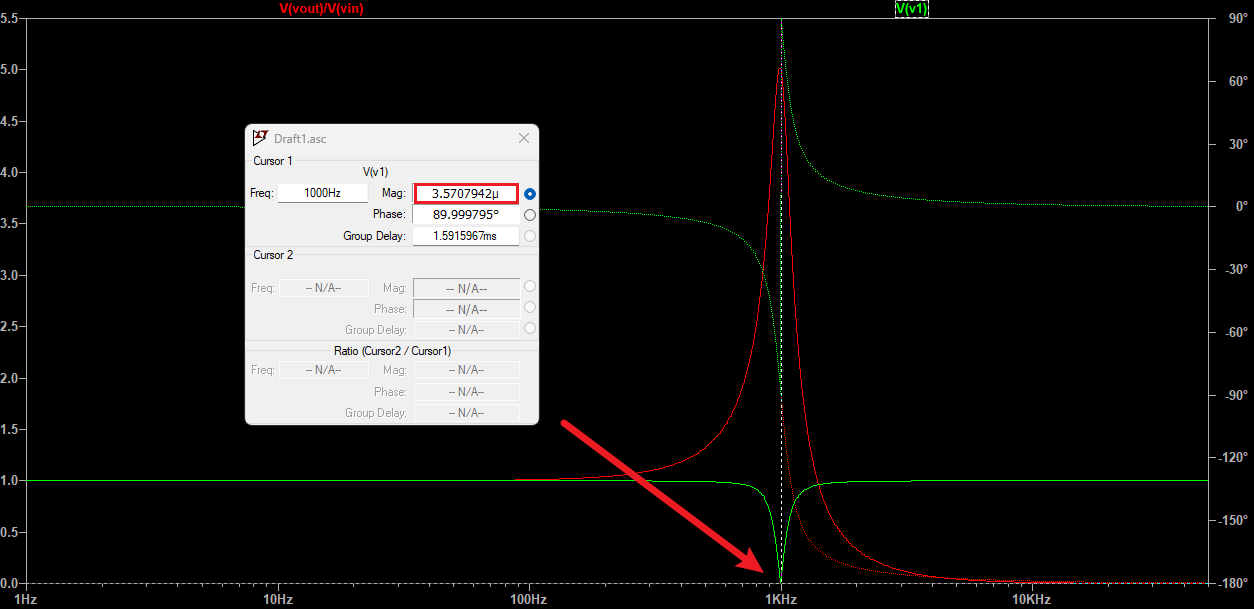

红色的部分代表了目前Vout和Vin比值,其受(R_1)服务器托管网大小的影响而变化,效果如下:

其大小随着电阻变化而变化,符合上式计算条件。

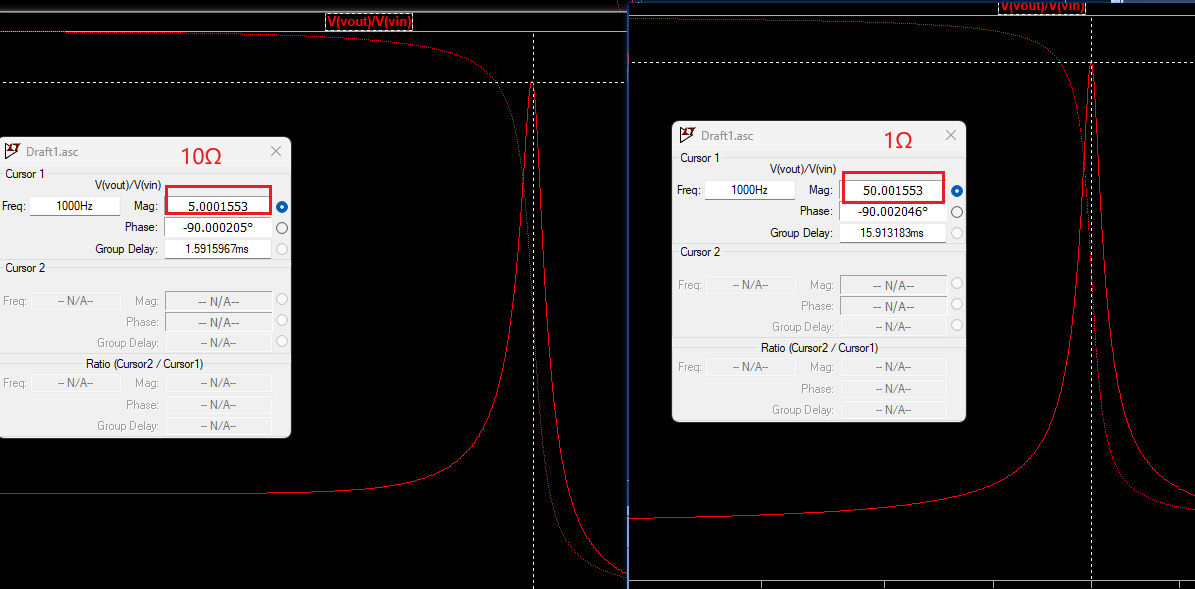

同时为了模拟常规的使用情况,和减少谐振点的影响,我们将信号源的内阻设定为50,滤波器负载后端的输出设置为50欧姆的阻抗来模拟网路的频幅特性曲线,如下图所示:

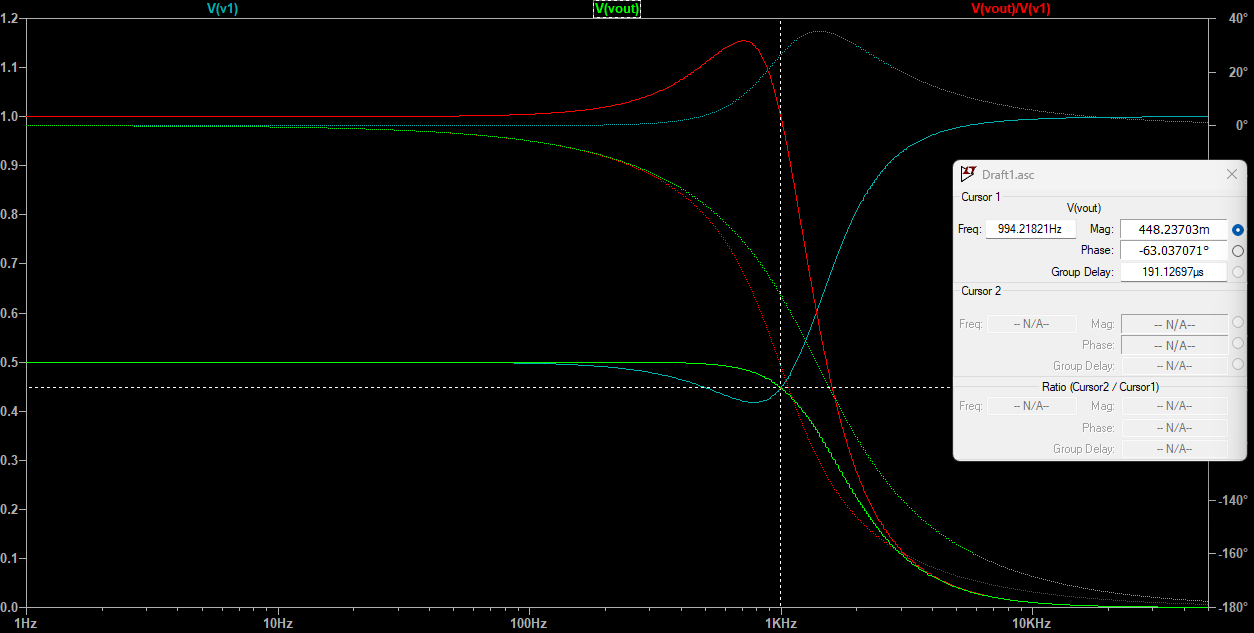

其幅频响应曲线如下图所示:

可以看到随着感抗的提升V1的电压随之提升,但容抗减小R2与C1构成的并联电路的阻抗大小随之减小,导致Vout持续下降,而V1持续上升,由于后端负载电路R2的存在导致红色部分Vout与V1的比值,也就是增益会有大于1的趋势,这并不是电路出现的问题,需要和上边的谐振问题分开来看待。

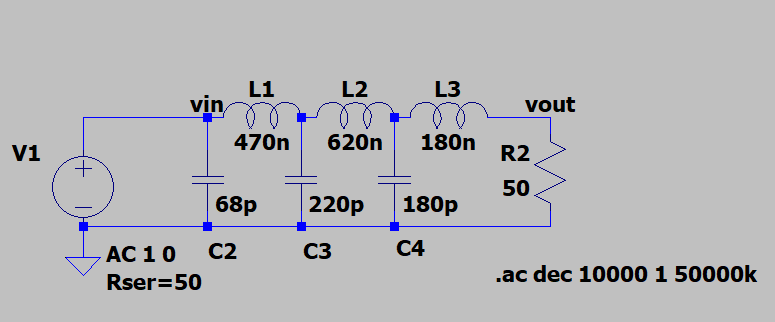

2、电路1仿真

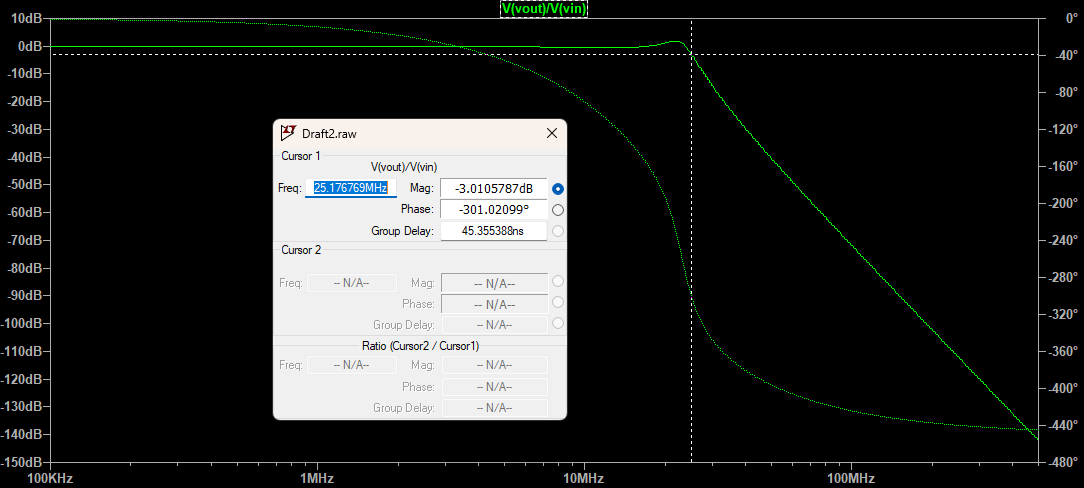

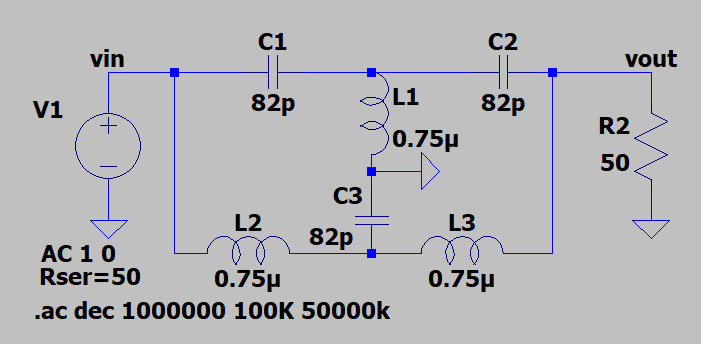

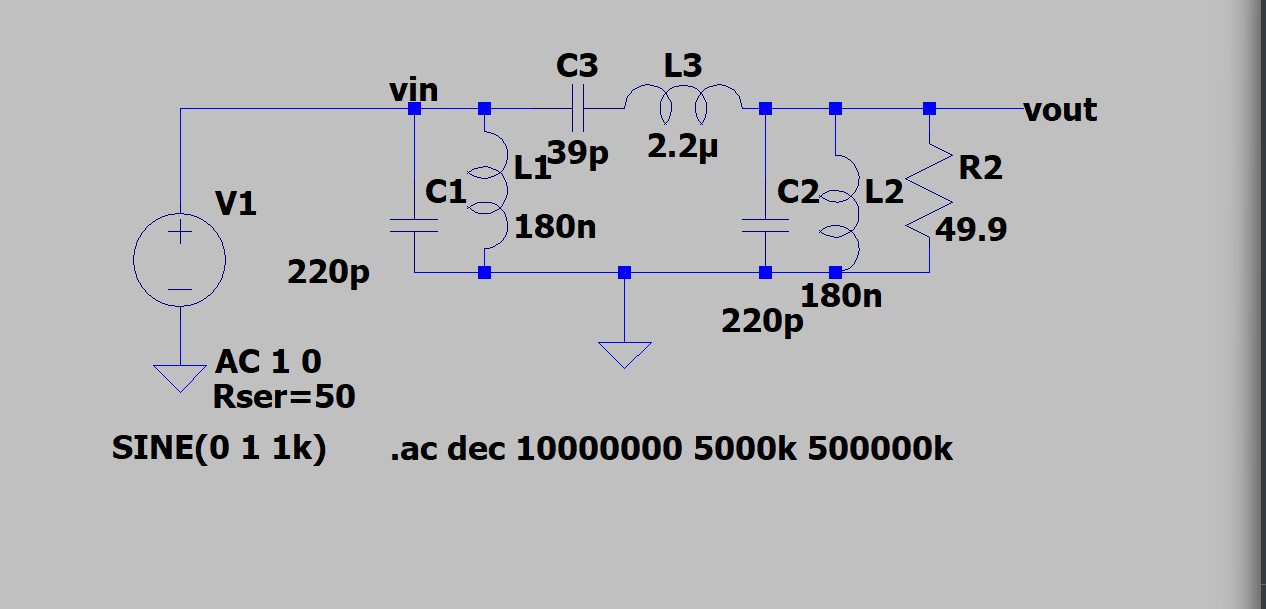

仍遵循50欧姆阻抗输入,50欧姆阻抗输出的默认条件,仿真其幅频特性

仿真其幅频特性横轴从100KHz至500Mhz,其基本频幅特性如下:

截止频率偏移至25Mhz左右。

3、电路2仿真

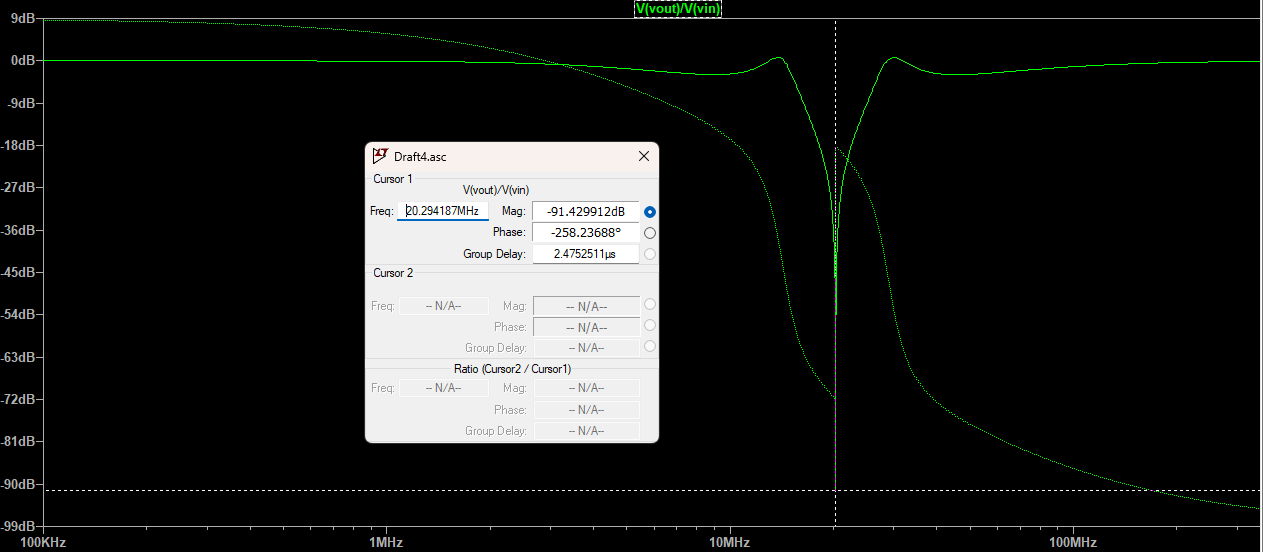

仍遵循50欧姆阻抗输入,50欧姆阻抗输出的默认条件。

仿真其幅频特性横轴从100KHz至500Mhz

其效果如下,为带陷滤波,中心频率为20Mhz左右。

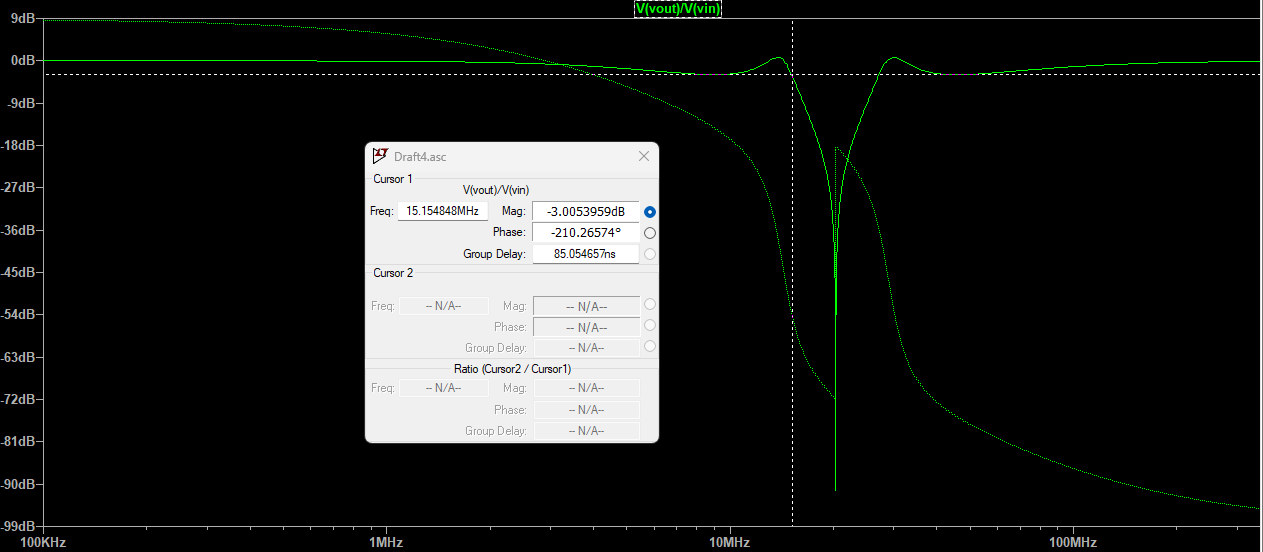

左-3dB频点:

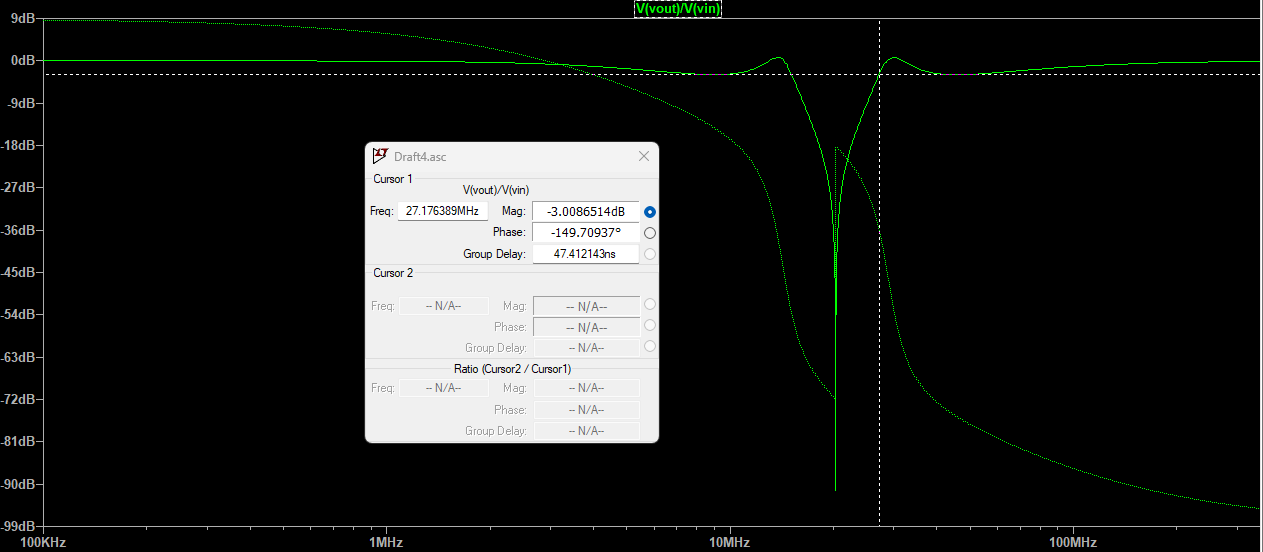

右-3dB频点:

模拟带陷带宽在15.15 ~ 27.176Mhz之间,大概12Mhz左右。

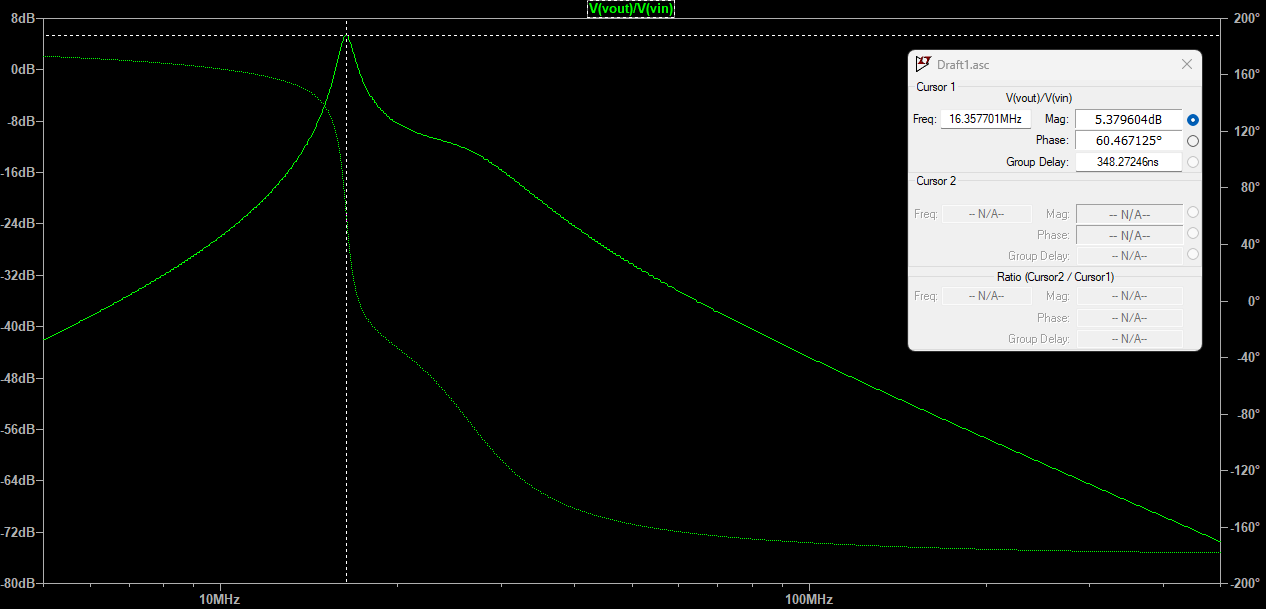

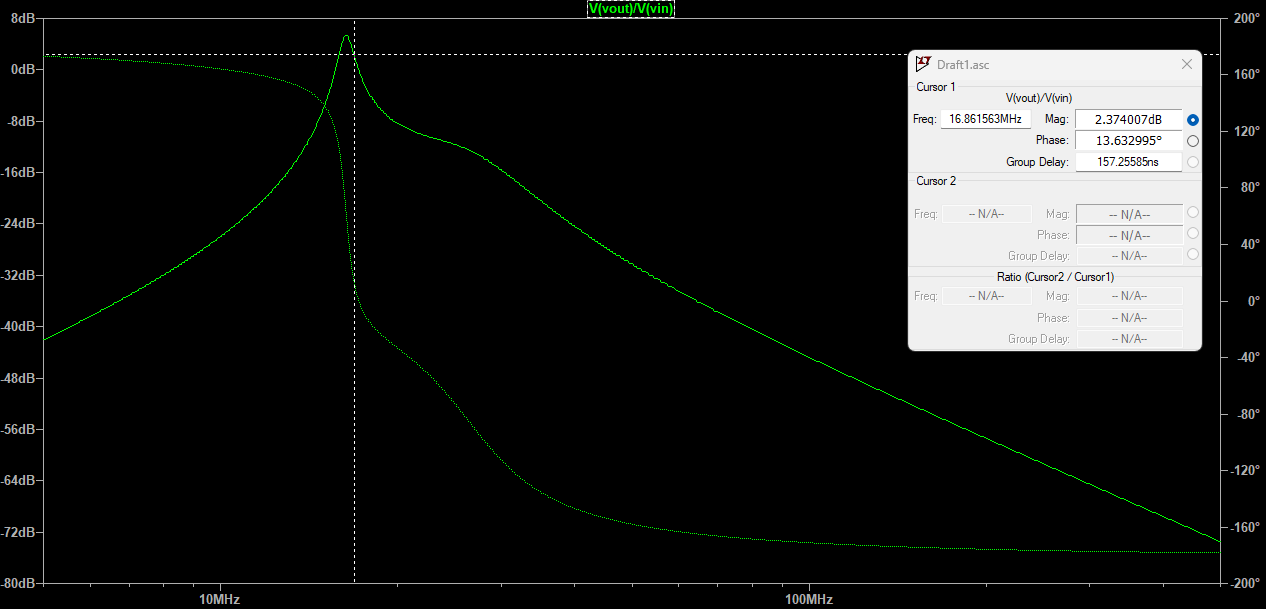

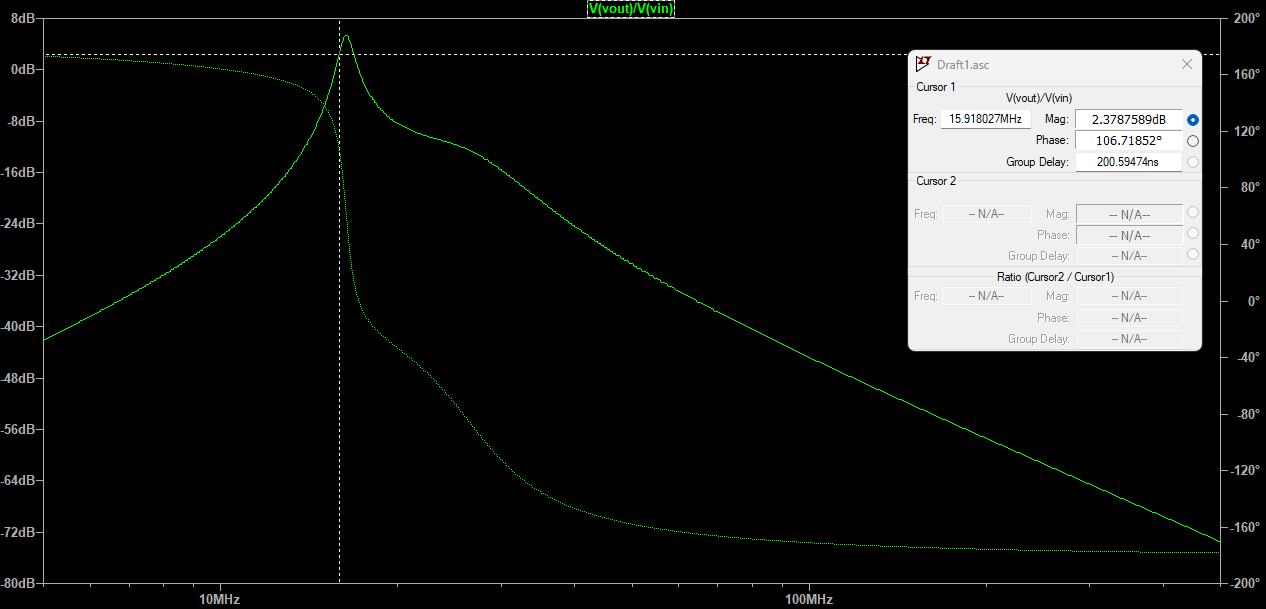

4、电路3仿真

仍遵循50欧姆阻抗输入,50欧姆阻抗输出的默认条件,仿真其幅频特性纵轴

电路如下:

本带通滤波系统下中心增益频率为:

右-3dB衰减频率为:

左-3dB衰减频率为:

模拟带通带宽在15.9~ 16.86Mhz之间,大概1Mhz左右。

服务器托管,北京服务器托管,服务器租用 http://www.fwqtg.net

机房租用,北京机房租用,IDC机房托管, http://www.fwqtg.net

相关推荐: “IDE 启动画面是如何诞生的?” | JetBrains AI 图形发展史

高春辉、王春生、朱峰:关于开源创业的15件小事 引入 上周的「1024 特别企划」推送中,我们分享了一套由 JetBrains 使用 AI 生成式技术创作的壁纸屏保。其实,JetBrains 在 AI 艺术方面的探索已经持续多年。大家熟悉的 IDE 启动画面正…