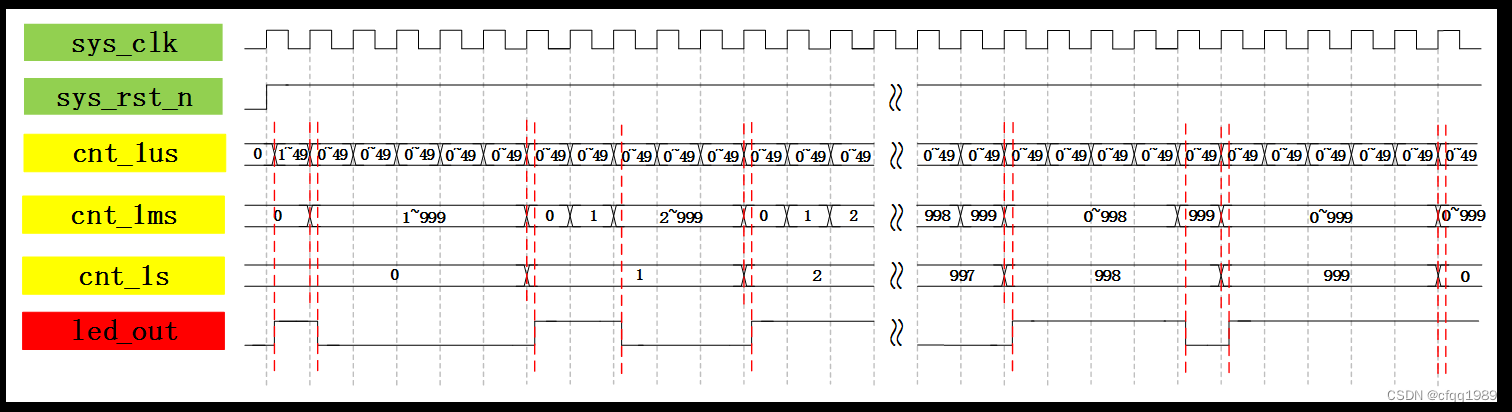

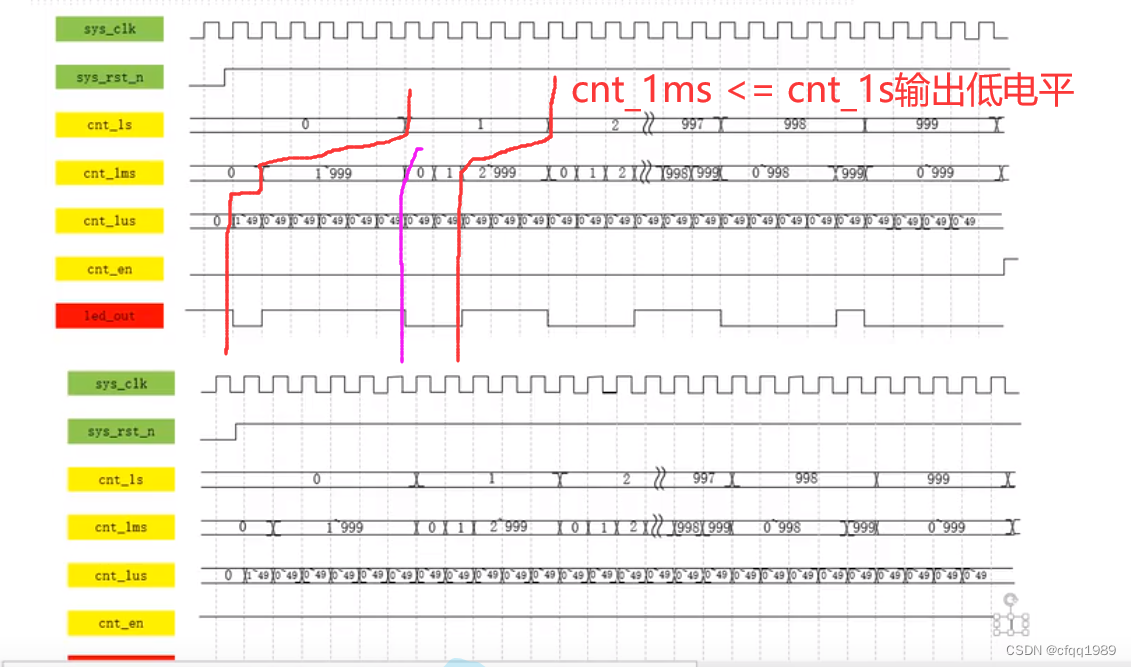

晶振50Mhz

1us等于计0~49

1ms等于 0~999us

1s等于 0~999ms

//led_out

always@(posedge FPGA_CLK_50M_b5 or negedge reset_e8) //【死循环】@敏感【触发条件:上升沿 clk】【运行副本】

if(reset_e8==1'b0)begin //50Mhz晶振, 49_999_999 是 1秒1次

led_out = cnt_1s ))// s满,

led_out

//======================================================

module sleep_led // 模块名字,参数,方法体

#(

parameter CNT_1US_MAX = 6'd49 ,

parameter CNT_1MS_MAX = 10'd999 ,

parameter CNT_1S_MAX = 10'd999

)

(

input FPGA_CLK_50M_b5,

input reset_e8,

input key1_k18,

input key2_n17,

input key3_n18,

input key4_h17,

//

output led1_d15,

output led2_c15,

output led3_a12,

output服务器托管网 led4_b12,

output beep_h13 //【注】最后一个参数不加逗号

);

//【】以下是变量

//

reg [5:0] cnt_1us;// 50Mhz晶振, 0~49

reg [9:0] cnt_1ms;

reg [9:0] cnt_1s;

reg [0:0] cnt_en;

reg [0:0] led_out;

//【】以下是方法体,FPGA的特性是程序都是并联运行。

//assign {led1_d15,led2_c15,led3_a12,led4_b12} = {~key1_k18,~key2_n17,~key3_n18,~key4_h17}; //key1_k18 +key2_n17 + key3_n18 +key4_h17 ;

//us

always@(posedge FPGA_CLK_50M_b5 or negedge reset_e8) //【死循环】@敏感【触发条件:上升沿 clk】【运行副本】

if(reset_e8==1'b0)begin //50Mhz晶振, 49_999_999 是 1秒1次

cnt_1us = cnt_1s ))// s满,

led_out 服务器托管,北京服务器托管,服务器租用 http://www.fwqtg.net

作者简介:练习时长两年半的Java up主 个人主页:程序员老茶 ps:点赞是免费的,却可以让写博客的作者开兴好久好久 系列专栏:Java全栈,计算机系列(火速更新中) 格言:种一棵树最好的时间是十年前,其次是现在 动动小手,点个关注不迷路,感谢宝子们一键三连…